[:en]Contacter Yves Blaquière (UQAM), blaquiere.yves@uqam.ca, local PK-4820

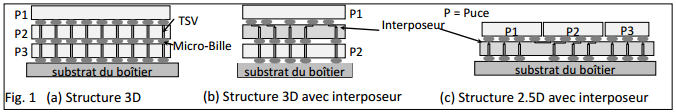

Description du projet: Les technologies d’encapsulation multidimensionnelle, tel l’empilement de dés de silicium (puces), permettent de réduire significativement les dimensions et le poids, tout en augmentant la fonctionnalité de systèmes électroniques modernes, tels les téléphones cellulaires. Elles intègrent dans un seul boîtier des processeurs, des mémoires, des capteurs, des antennes, des dispositifs hétérogènes et électromécaniques, et permettent un très grand nombre de terminaux électriques et optiques entre eux. Ce grand nombre de terminaux est rendu possible entre autres par l’exploitation des techniques récentes de perçage du silicium (Through Silicon Vias, TSVs). Pour faciliter l’intégration, des interposeurs passifs en silicium avec TSVs et plusieurs couches de métallisation sont construits pour s’aligner aux patrons de terminaux (billes, plots) de chaque dé de silicium, et utilisés comme structure passive d’interconnexions entre les puces. Ces technologies d’encapsulation multidimensionnelle présentent plusieurs défis additionnels, entre autres de fiabilité (rendement, gestion thermique, dissipation de puissance, alignement des puces), de testabilité, de diagnostic et de coûts.

Le programme de recherche vise à réduire les risques et les incertitudes pour rendre configurables les technologies d’encapsulation multidimensionnelle. L’originalité consiste en la création d’un interposeur actif intelligent peuplée d’une mer de plots configurables de très petites dimensions, telles qu’un ou plusieurs plots puissent être électriquement connectés à un TSV ou une micro-bille de la puce en contact. L’élaboration d’un réseau d’interconnexions configurables permettrait de relier n’importe quels plots ou TSVs de l’interposeur aux autres. Cette propriété de configuration ouvrira les portes vers un prototypage plus rapide et rendra l’assemblage insensible à l’alignement des plots avec une réduction significative des coûts de réalisation et de test.

Compétences recherchées des candidats

- Connaissance détaillée du flot de conception de circuits intégrés : VHDL, Synthèse, Cadence;

- Design de circuits intégrés mixtes (logique et analogique) : placement et routage, réseau de distribution des alimentations, génération d’arbres d’horloge, vérification, dessin des masques.

- Autonome, aime les défis et les technologies de pointe.

[:fr]Contacter Yves Blaquière (UQAM), blaquiere.yves@uqam.ca, local PK-4820

Description du projet: Les technologies d’encapsulation multidimensionnelle, tel l’empilement de dés de silicium (puces), permettent de réduire significativement les dimensions et le poids, tout en augmentant la fonctionnalité de systèmes électroniques modernes, tels les téléphones cellulaires. Elles intègrent dans un seul boîtier des processeurs, des mémoires, des capteurs, des antennes, des dispositifs hétérogènes et électromécaniques, et permettent un très grand nombre de terminaux électriques et optiques entre eux. Ce grand nombre de terminaux est rendu possible entre autres par l’exploitation des techniques récentes de perçage du silicium (Through Silicon Vias, TSVs). Pour faciliter l’intégration, des interposeurs passifs en silicium avec TSVs et plusieurs couches de métallisation sont construits pour s’aligner aux patrons de terminaux (billes, plots) de chaque dé de silicium, et utilisés comme structure passive d’interconnexions entre les puces. Ces technologies d’encapsulation multidimensionnelle présentent plusieurs défis additionnels, entre autres de fiabilité (rendement, gestion thermique, dissipation de puissance, alignement des puces), de testabilité, de diagnostic et de coûts.

Le programme de recherche vise à réduire les risques et les incertitudes pour rendre configurables les technologies d’encapsulation multidimensionnelle. L’originalité consiste en la création d’un interposeur actif intelligent peuplée d’une mer de plots configurables de très petites dimensions, telles qu’un ou plusieurs plots puissent être électriquement connectés à un TSV ou une micro-bille de la puce en contact. L’élaboration d’un réseau d’interconnexions configurables permettrait de relier n’importe quels plots ou TSVs de l’interposeur aux autres. Cette propriété de configuration ouvrira les portes vers un prototypage plus rapide et rendra l’assemblage insensible à l’alignement des plots avec une réduction significative des coûts de réalisation et de test.

Compétences recherchées des candidats

- Connaissance détaillée du flot de conception de circuits intégrés : VHDL, Synthèse, Cadence;

- Design de circuits intégrés mixtes (logique et analogique) : placement et routage, réseau de distribution des alimentations, génération d’arbres d’horloge, vérification, dessin des masques.

- Autonome, aime les défis et les technologies de pointe.

[:]